本文简述常规MOSFET开关阈值的基本原理与影响因素

MOS电容

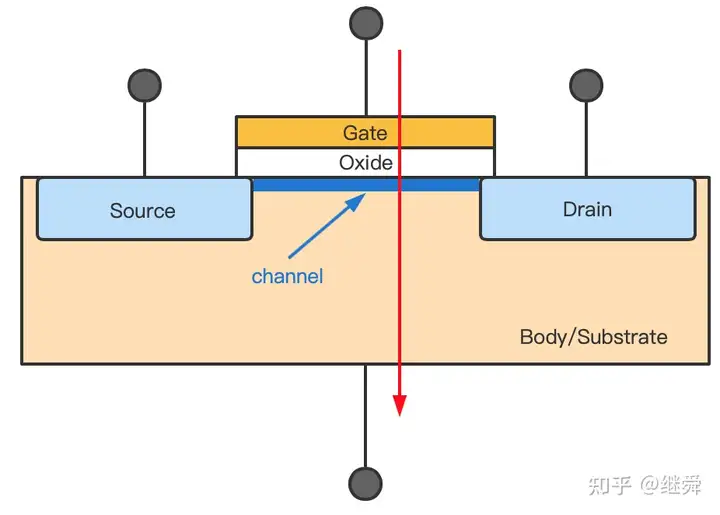

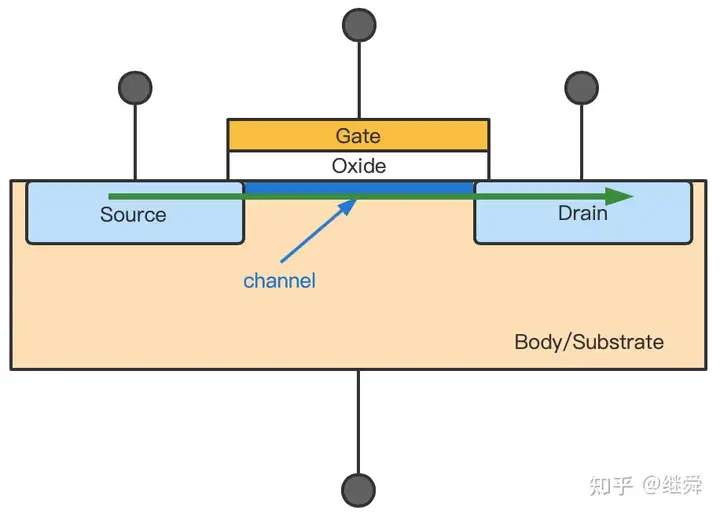

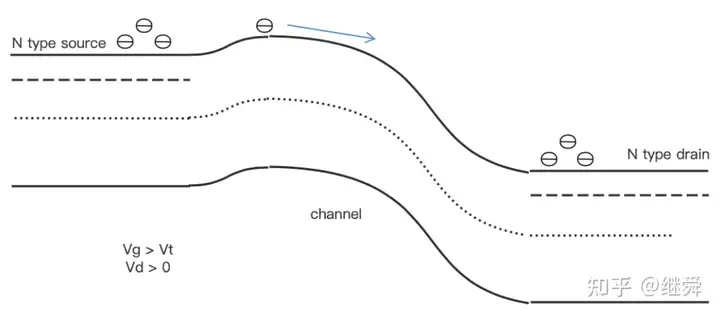

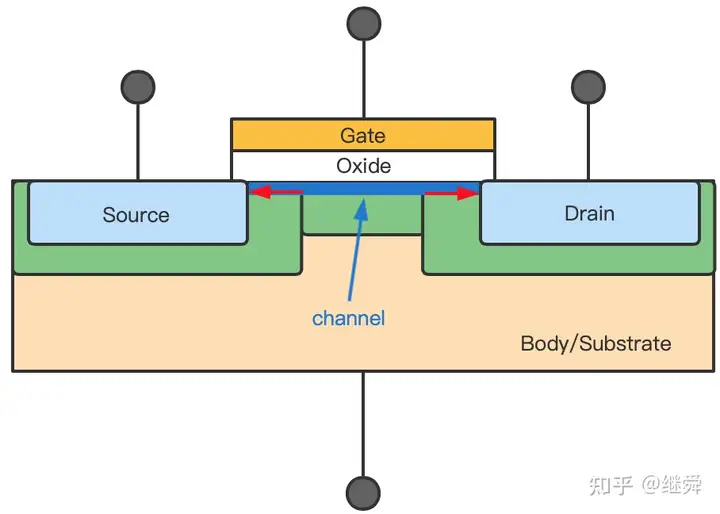

以N沟道增强型MOSFET为例(下同),MOSFET是通过半导体靠近栅极的位置形成导电沟道来实现连通源极与漏极以实现开关作用的。

如上图中所示(沿红色箭头),栅极与衬底成为电容(MOS电容)的两个极板,中间氧化物绝缘体为电介质。电压加到栅极与衬底之间,在两个极板上累积电荷,在衬底半导体一侧累积的可移动电荷形成导电沟道。

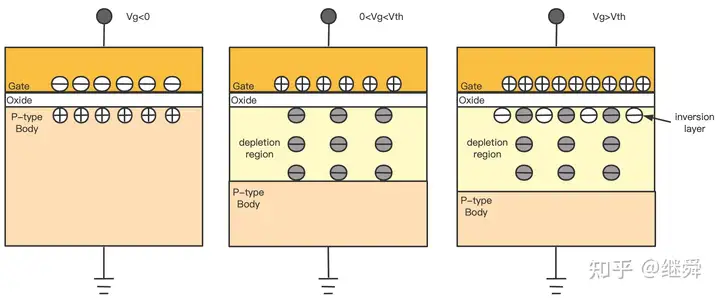

MOS电容在不同栅极电压下的电荷分布示意图如下(1.衬底电压为零作为参考点;2.灰色为不可移动电荷):

Vg栅极电压为负时,P型半导体内的正电荷(空穴,多数载流子)在靠近栅极的表面很薄一层大量汇集,但这不是MOSFET工作状况,不作讨论。

Vg电压为正,但比较小,没有超过阈值电压。栅极的正电荷排斥衬底中的空穴,留下了带负电的掺杂离子,此时没有可自由移动的电荷,没有导电通道。

Vg超过阈值电压后,半导体表面累积了可移动的载流子电荷,形成反型层导电沟道(电子代替空穴成为多数载流子,所以称为反型)。

那么,阈值电压多大呢?

MOS电容能带结构

在之前的文章继舜:肖特基势垒与欧姆接触中介绍过半导体的能带结构,可以继续使用该模型理论分析MOS电容。

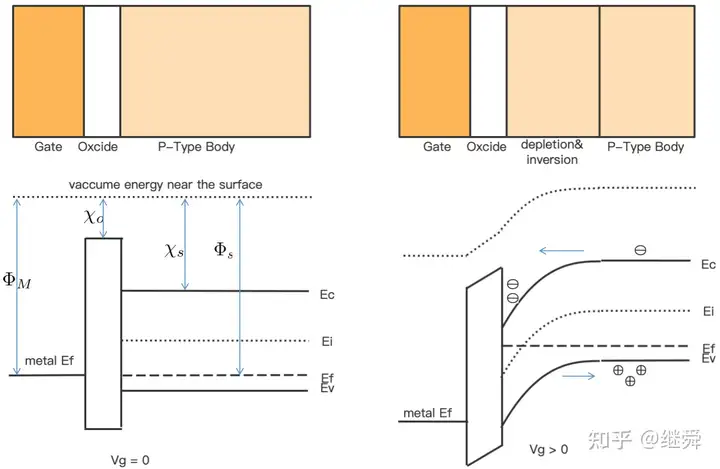

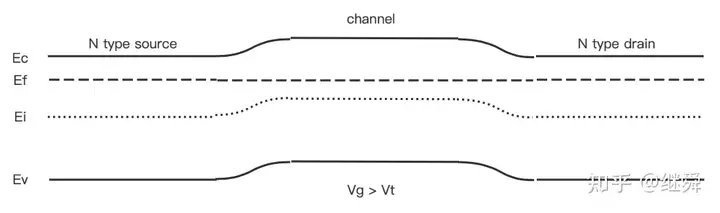

假设栅极与衬底的费米能级相同(后面分析不同时的情况),MOS电容静态时与栅极加正电压时的能带示意图如下:

静态时氧化层两侧费米能级相同,无电荷积累,能带平直。

栅极加正电压,其能级被压低,在氧化层中和半导体中存在电场,能带偏斜弯曲。氧化层中没有电荷分布,存在恒定电场,半导体中存在电荷分布,电场强度随位置变化。

半导体中电荷(载流子)分布与其能级相关,如下式:

p=ni⋅e(Ei−EF)/kTn=ni⋅e(EF−Ei)/kT p=n_i\cdot e^{(E_i-E_F)/kT} \\ n=n_i\cdot e^{(E_F-E_i)/kT}

在P型衬底中,空穴浓度大小取决于能带图中硅本征半导体费米能级Ei与实际掺杂半导体费米能级Ef之间的差值。在靠近栅极的半导体表面,能带弯曲,实际费米能级高于本征费米能级,此时该位置的电子要多于空穴,当电子浓度与远处衬底内空穴浓度相同时,称此时表面形成了反型层(因为这个位置电子浓度与空穴浓度翻转了)。

出现反型层之后,如果进一步增加栅极电压,会有大量电子在半导体表面很薄一层内聚集,而不会进一步扩大耗尽区,因为这时电子已经成为多数载流子,其表现的像N型半导体。

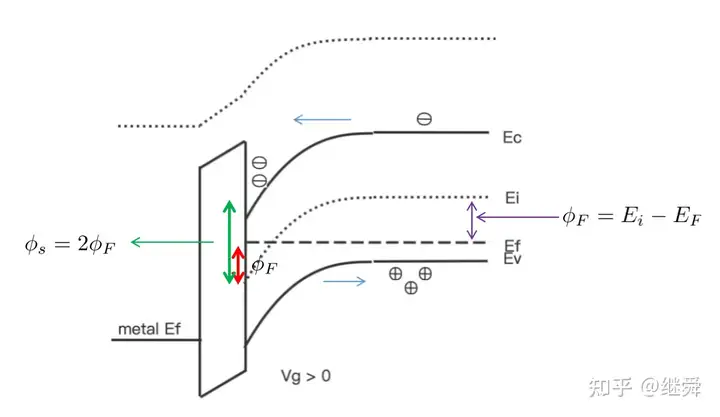

所以阈值电压的大小就是使半导体表面电势与衬底参考电势差值为:

ϕs=2ϕF\phi_s=2\phi_F

而后者取决于衬底半导体的掺杂浓度相关。

确定了半导体表面电势之后还需要确定氧化层中的电势差才能最终确定阈值电压(栅极电势与衬底参考电势的差值),因为氧化层中为恒定强度电场,所以氧化层两侧电势差与氧化层厚度及氧化层介电常数相关。阈值电压公式如下(本文重在理解,不作详细推导)

VT=2ϕF+KSxoKo4qNAKSε0ϕFKS:SemiconductordielectricalcoefficientKo:Oxidedielectricalcoefficientxo:OxidelayerthicknessV_T=2\phi_F+\frac{K_S x_o}{K_o}\sqrt{\frac{4qN_A}{K_S \varepsilon_0}\phi_F}\\ K_S: Semiconductor\space dielectrical\space coefficient \\ K_o: Oxide\space dielectrical\space coefficient \\ x_o: Oxide\space layer\space thickness

Gate材料对阈值电压的影响

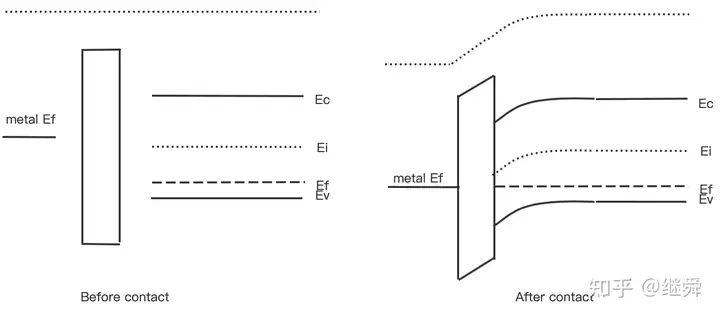

前面假设金属栅极材料的费米能级与半导体的费米能级相同,组成MOS电容后能带平直,实际上两者并不同。下图为不同时的能带图示例。

在未加栅极电压时,半导体内部已经存在了内建电场和能带弯曲,以上图为例,相对于理想情况,加更少的栅级电压即可形成反型层,即阈值电压更小。

MOSFET二维能带结构

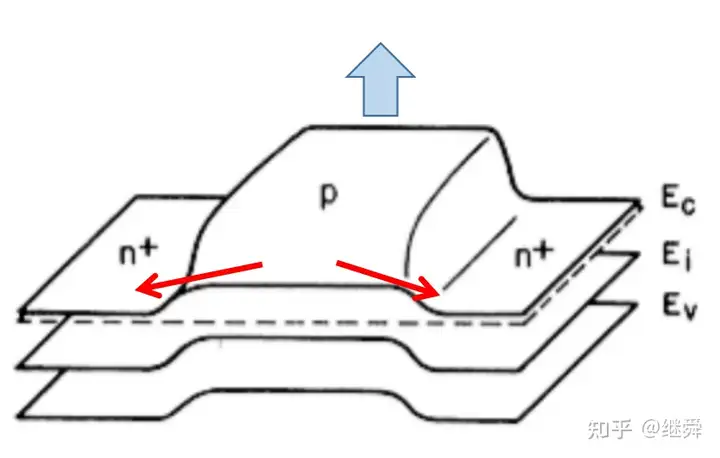

前面只讨论了栅极与衬底形成的MOS电容,下面再看一下水平方向的源-沟道-漏方向的能带结构(下图绿色箭头)。

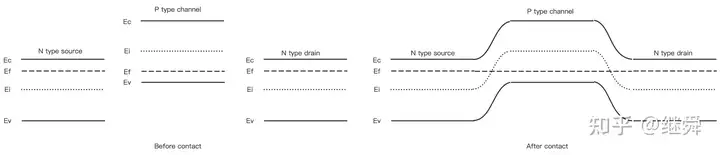

其能带结构如下:

在没加栅极电压时,P型材料的沟道区域形成高高的势垒,阻止源极与漏极之间电子的相互流动,此时MOSFET为关断状态。

栅极加上大于阈值的电压后,其能带如下:

沟道中的势垒降低,电子可以跃过,实现导能,此时MOSFET处于导通状态。漏极加上电压后能带图如下:

备注:此时因为有电流存在,所以费米能级不保持平直。

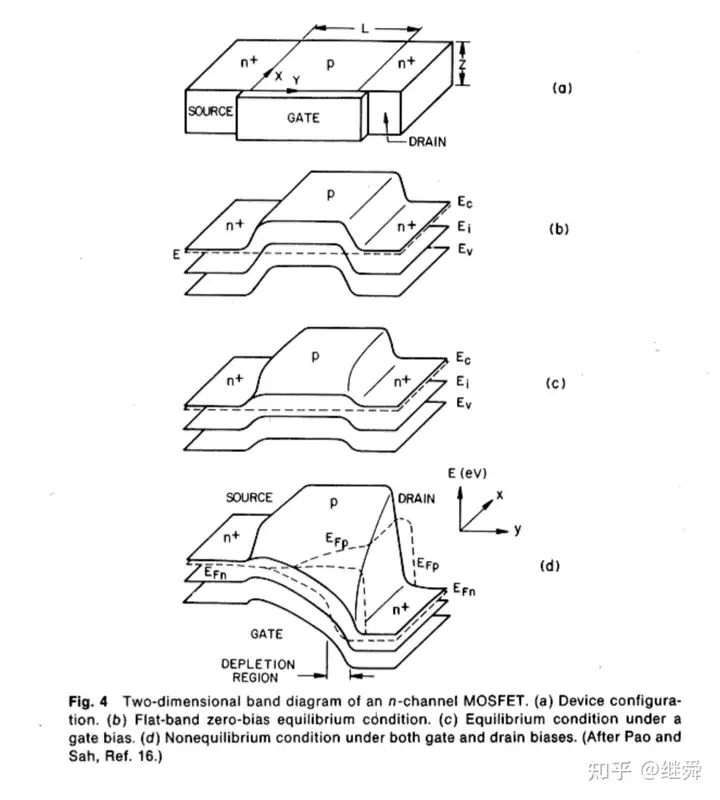

综合前面垂直与水平两个方向,可以得到MOSFET的二维能带结构图如下:

图11-a为MOSFET模型结构;图11-b为静态情况下的二维能带结构;图11-c为栅极加电压后在半导体表面形成沟道;图11-d为漏极加电压后的二维能带结构。

衬底偏置对阈值电压的影响

通常MOSFET都会假设将衬底连接到源极,但有时在衬底使用不一样的电压可以改变MOSFET开关阈值电压值。

对于一维的MOS电容来说,形成反型层的电压只与栅极和衬底的电压差有关。但是二维的MOSFET则不同,如下图示例,衬底加负电压,会抬高中间沟道区域的势垒,这样本来在表面形成的反型层电子会流向更低的源极或漏极,使得反型层消失,只有加更大的栅极电压才能再次形成反型层,即衬底加负电压增大了阈值电压。

另一个角度来看这个现象,如下图绿色为衬底与源极漏极之间的PN结耗尽区,衬底加负电压即该PN结反偏,会增大耗尽区,增大的耗尽区中更大的内建电场会让沟道中的电子流向源极与漏极,沟道中电子减少,沟道导电能力下降。

其它影响因素

还有很多工艺相关的因素(如氧化层电荷)可以极大的影响阈值电压,但不在本文讨论范围之内。

Reference:

Semiconducctor Device Fundamentals, Robert F. Pierret;

Essential physics of the MOSFET, Mark Lundstorm;

免责声明:文章内容来自互联网,本站仅作为分享,不对其真实性负责,如有侵权等情况,请与本站联系删除。

转载请注明出处:理解MOSFET阈值电压 https://www.zentong.com/zt/8882.html