一块巴掌大的电路板,可能藏着上百个焊点、数十条走线,却能支撑起一台智能设备的核心运算。在它从图纸变成实物的过程中,PCB 打样扮演着不可替代的角色。这个看似简单的环节,既是对设计方案的第一次 “体检”,也是决定产品能否顺利量产的关键伏笔。无论是消费电子的创新迭代,还是工业设备的稳定运行,都离不开 PCB 打样阶段的反复打磨。

(此处可插入图片:PCB 打样车间一角,工程师正在用放大镜检查刚出炉的样板,灯光下电路板的走线清晰可见,旁边放着设计图纸和检测仪器)

PCB 打样,通俗来说就是小批量制作电路板样板,目的是验证设计方案的可行性。不同于量产阶段的标准化生产,打样更像是一场 “摸着石头过河” 的探索 —— 设计师需要通过样板测试电路的稳定性、信号的传输效率,甚至是元件的排布是否合理。曾经有一家智能手表厂商,在打样阶段发现某条高频信号线与电源走线距离过近,导致信号干扰严重,最终通过调整布线方式解决了问题。若是直接跳过打样进入量产,这样的设计缺陷可能造成数千万元的损失。

设计审核是 PCB 打样的第一道关卡,也是最容易被忽视的环节。经验丰富的打样工程师,会像侦探一样审视每一份设计文件。他们会重点检查走线的宽度是否符合电流承载需求 —— 比如通过 1A 电流的走线,宽度至少要达到 0.3mm,若涉及高频信号,还需考虑阻抗匹配;焊盘的大小是否适配元件引脚,避免出现虚焊或焊点过大的问题;过孔的数量和位置是否合理,防止信号传输时出现 “瓶颈”。某新能源汽车的 BMS(电池管理系统)PCB 打样时,设计文件中过孔直径仅 0.2mm,而工厂的钻孔精度下限是 0.25mm,工程师及时反馈后,设计师将过孔直径调整至 0.3mm,避免了样板制作失败。

材料的选择直接影响 PCB 样板的性能,却没有统一的标准答案。覆铜板是电路板的 “骨架”,FR-4 材质因性价比高成为常规选择,但在高温环境下工作的设备,比如汽车发动机舱内的控制板,就需要改用耐温性更强的 PI 材质,其长期使用温度可达 130℃以上。铜箔厚度的选择同样有讲究:普通消费电子的 PCB 多采用 1 盎司铜箔(约 35μm 厚),而需要通过大电流的电源板,可能要用到 2 盎司甚至 4 盎司铜箔。一位从事工业机器人研发的工程师分享过经历:他们曾为了降低成本选择 1 盎司铜箔制作驱动板样板,测试时发现大电流通过时铜箔发热严重,最终换成 2 盎司铜箔才解决问题。

制板工艺的精度,决定了样板能否真实还原设计意图。蚀刻环节是控制精度的关键,先进的激光直接成像技术(LDI)能将线宽精度控制在 ±0.02mm 以内,这意味着即使是头发丝 1/3 粗细的走线,也能清晰成型。而传统的曝光显影工艺,精度往往只能达到 ±0.05mm,更适合对精度要求不高的简单电路。阻焊层的涂覆同样有讲究,哑光阻焊层能减少反光,适合需要光学检测的样板;亮光阻焊层则更耐磨,常用于经常插拔的接口板。有一家医疗设备公司,曾因打样时选用了普通阻焊层,导致样板在消毒水浸泡测试中出现涂层脱落,后来改用防化学腐蚀的专用阻焊层才通过验证。

测试环节是 PCB 打样的 “终极大考”,任何细微的缺陷都可能被放大。导通测试是基础,通过探针接触每个焊点,检测电路是否存在短路或断路;绝缘电阻测试则能发现走线之间的漏电隐患,确保在高湿度环境下的安全性。对于高频电路样板,还需要进行信号完整性测试,用网络分析仪测量传输线的插入损耗和回波损耗,确保信号在传输过程中不会失真。某 5G 基站射频板的打样中,测试发现某段微带线的回波损耗超标,工程师通过调整线长和阻抗匹配,最终将指标控制在合格范围内。

不同行业对 PCB 打样的需求千差万别,考验着打样服务商的灵活性。消费电子领域追求快速迭代,往往要求 24 小时内完成打样,甚至出现了 “48 小时加急” 的服务 —— 从收到设计文件到交付样板,全程不超过两天。工业控制领域则更看重稳定性,部分客户会要求样板经过 – 40℃至 85℃的高低温循环测试,验证其在极端环境下的可靠性。医疗设备领域的要求更为严苛,除了电气性能,还需满足生物相容性认证,所用材料不能释放有害物质。一家生产血糖仪的企业,在打样时就特别要求 PCB 表面处理采用无铅化工艺,避免重金属对检测结果的干扰。

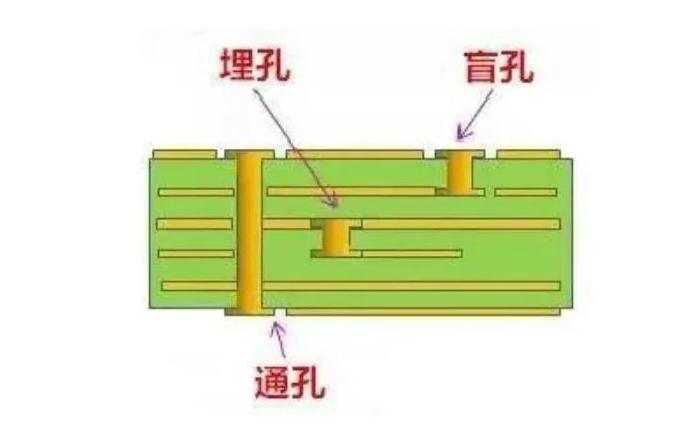

技术的迭代正不断重塑 PCB 打样的边界。柔性 PCB 打样近年来需求激增,这种可以弯曲的电路板,让智能手环、折叠屏手机等产品成为可能。打样时,柔性板的基材韧性测试是重点,需要反复折叠数千次后仍保持电路导通。高密度互联(HDI)技术则让 PCB 样板向 “微型化” 发展,通过盲孔、埋孔技术减少过孔占用的空间,使相同面积的电路板能容纳更多元件。某无人机厂商通过 HDI 打样,将飞控板的尺寸缩小了 30%,大大提升了无人机的续航能力。

成本控制是 PCB 打样中绕不开的话题,却不是简单的 “越便宜越好”。影响打样成本的因素包括样板尺寸、层数、工艺复杂度和交期 —— 一块 10cm×10cm 的 4 层板,加急打样的价格可能是普通交期的两倍。有经验的研发团队会在设计阶段就考虑打样成本:比如将电路板尺寸控制在标准范围内(如 10cm×10cm 以内),避免因 “非标尺寸” 产生额外费用;减少不必要的异形孔,选择常规表面处理工艺(如沉金、喷锡)而非特殊工艺。但节省成本的前提是不影响测试需求,曾有创业公司为了省钱,将 6 层板设计简化为 4 层板打样,结果因信号干扰无法完成测试,反而耽误了研发进度。

PCB 打样的过程,也是设计师与打样工程师碰撞协作的过程。优秀的打样工程师不仅是 “执行者”,更是 “建议者”。他们会根据工厂的设备能力,为设计师提供可制造性建议 —— 比如某款智能家居控制板的设计中,设计师原本在角落布置了密集的元件,工程师建议适当分散,避免焊接时出现 “阴影效应”;某传感器 PCB 的走线过于纤细,工程师提醒可能在后续装配中被轻易刮断,最终设计师调整了走线宽度。这种协作能大幅提升打样成功率,缩短研发周期。

从一张二维设计图到一块能稳定工作的电路板,PCB 打样就像一场精密的 “翻译”—— 将抽象的设计语言转化为具象的物理实体。每一个焊点的饱满度、每一条走线的流畅度,都承载着研发团队的创新构想。随着电子技术向更智能、更精密的方向发展,PCB 打样也将面临更多新的挑战:如何应对更高的信号频率、如何适应更复杂的散热需求、如何匹配更严苛的环保标准…… 而这些挑战,或许正是推动电子产业不断向前的动力。

免责声明:文章内容来自互联网,本站仅提供信息存储空间服务,真实性请自行鉴别,本站不承担任何责任,如有侵权等情况,请与本站联系删除。