D触发器的工作原理及应用

在数字系统中,触发器是一种重要的基本单元,它能够存储一位二进制信息,并且具有在外部信号的作用下改变其存储状态的能力。D触发器,全称为数据触发器或延迟触发器,是一种常用的触发器类型。

D触发器的基本概念

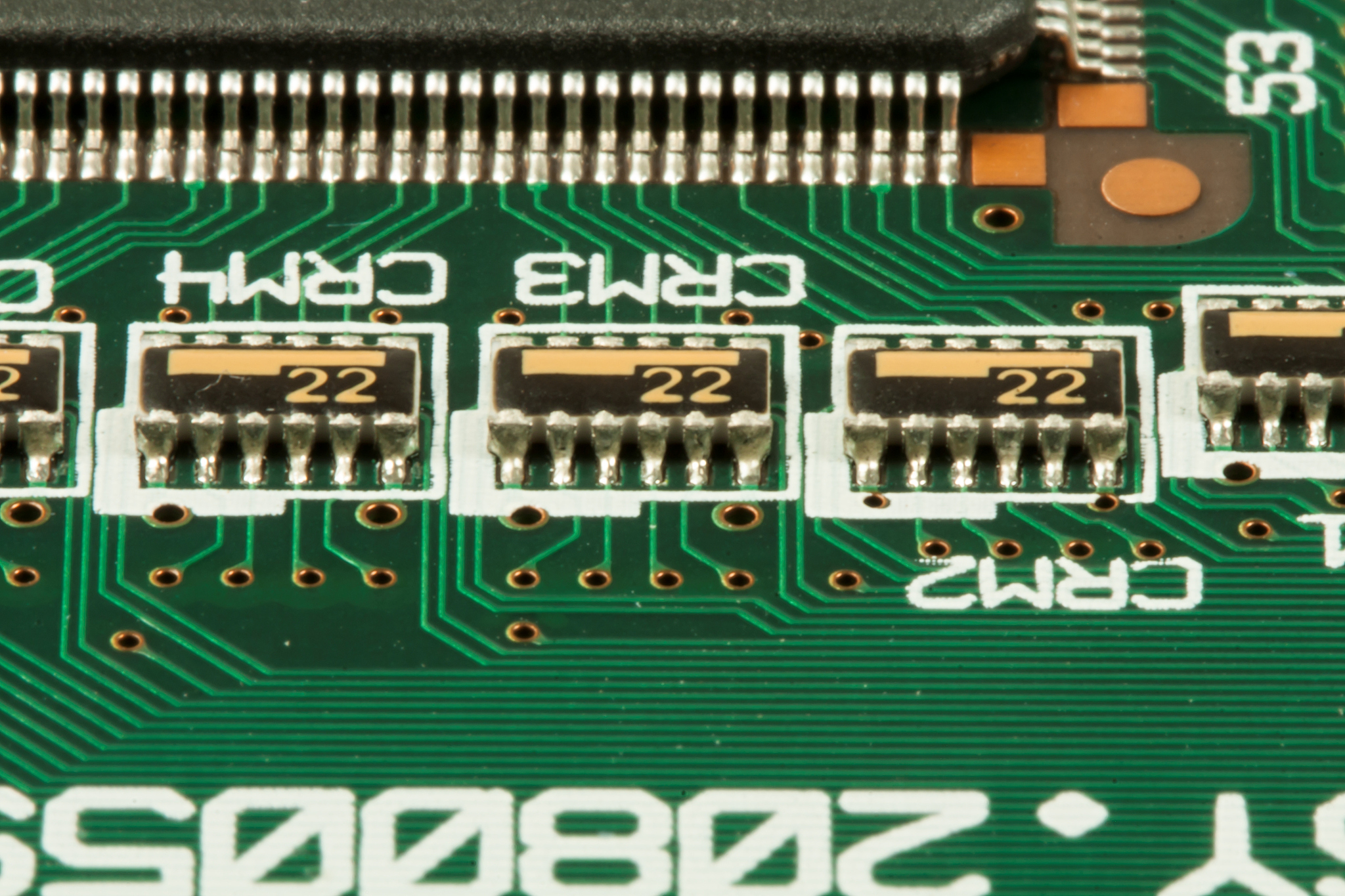

D触发器是一种具有置位、复位和保持功能的触发器。它仅有一个输入端D(Data),一个输出端Q,以及一个时钟输入端CLK。在上升沿触发时,D端的数据会被存储在触发器中,并从Q端输出。

D触发器的工作原理

D触发器的工作原理是基于存储单元的读写操作。在时钟信号CLK的作用下,D端的数据会在上升沿时刻被写入存储单元中,并从Q端输出。这个过程可以分为三个阶段:

输入阶段:在时钟信号为低电平期间,D端可以输入数据,此时触发器处于等待状态。

触发阶段:当时钟信号上升沿到来时,D端的数据会被写入存储单元中。此时,触发器输出状态与D端输入状态相同。

保持阶段:在时钟信号为高电平期间,触发器会保持之前的状态不变,直到下一个时钟信号的上升沿到来。

D触发器的应用

D触发器在数字系统中有着广泛的应用,主要包括以下几个方面:

寄存器:D触发器可以组成寄存器,用于存储二进制数据。在时钟信号的上升沿时刻,输入的数据会被写入寄存器中,并从输出端读取出来。

计数器:通过将多个D触发器级联起来,可以组成计数器。在每个时钟周期的上升沿时刻,计数器的值会自动加1。这种方法可以用于实现定时器、计时器等功能。

移位寄存器:将多个D触发器首尾相连,可以组成移位寄存器。在时钟信号的作用下,数据会沿着移位寄存器向左或向右移动一位。这种方法可以用于实现串行数据的传输和控制。

状态机:通过将多个D触发器和组合逻辑电路组合起来,可以构成状态机。状态机是一种具有有限个状态的控制单元,它根据当前的状态和输入信号来确定下一个状态。这种方法可以用于实现数字系统的控制逻辑。

D触发器是一种常用的数字逻辑元件,它具有简单的结构和广泛的应用领域。了解和掌握D触发器的工作原理和基本概念对于数字系统设计和开发人员来说非常重要。在实际应用中,需要根据具体的需求选择合适的D触发器类型和规格,并配合其他数字元件来实现所需的数字系统功能。随着数字技术的不断发展,D触发器的应用前景仍然十分广阔,特别是在嵌入式系统和计算机硬件等领域中具有广泛的应用价值。