英特尔向今年的国际电子器件会议(IEDM)提交了几篇研究论文,强调了他们追求新的2D晶体管材料和3D封装解决方案的计划。这些新信息支持了首席执行官Pat Gelsinger之前关于英特尔即将进行的微架构设计创新的声明。据英特尔的Gary Patton称,新的进展将在可预见的未来保持摩尔定律的活力。

今年早些时候,NVIDIA的黄仁勋在4000系列发布会的问答环节中再次宣布摩尔定律已死。这一预测与他在2017年北京GPU技术大会上的类似声明相呼应。

该公司提交的2023年IEDM研究报告强调了几种工艺、材料和技术,可以帮助这家半导体巨头支持他们之前关于到2030年交付基于芯片的万亿晶体管处理器。

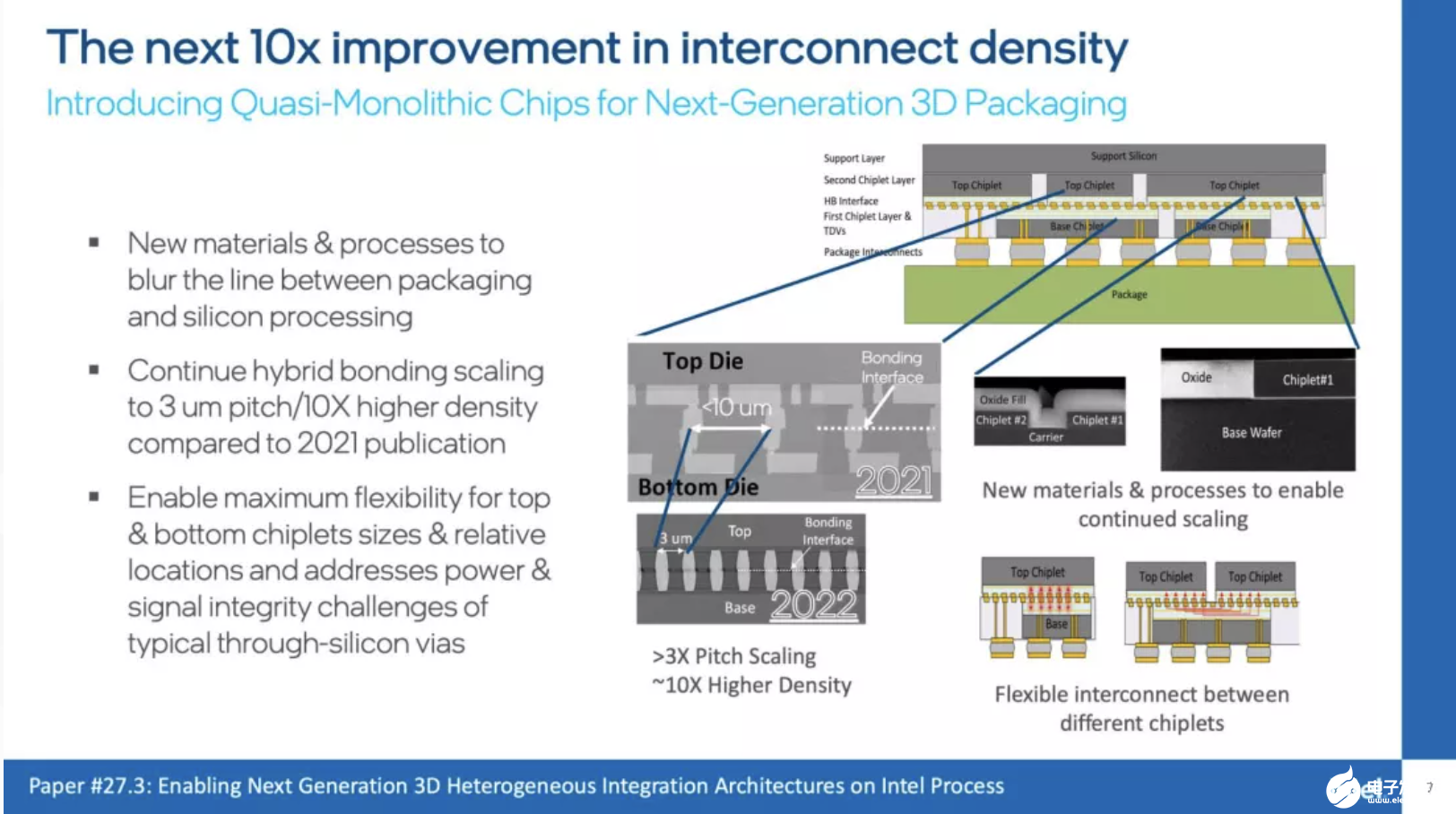

英特尔的新晶体管和封装技术研究主要集中在推进CPU的性能和效率,缩小传统单片处理器和基于芯片的新设计之间的距离。提交的材料中提出的一些概念包括:大大减少小芯片之间的间隙以提高性能,即使在失去电源后也能保持其状态的非易失性晶体管,以及新的可堆叠存储器解决方案。

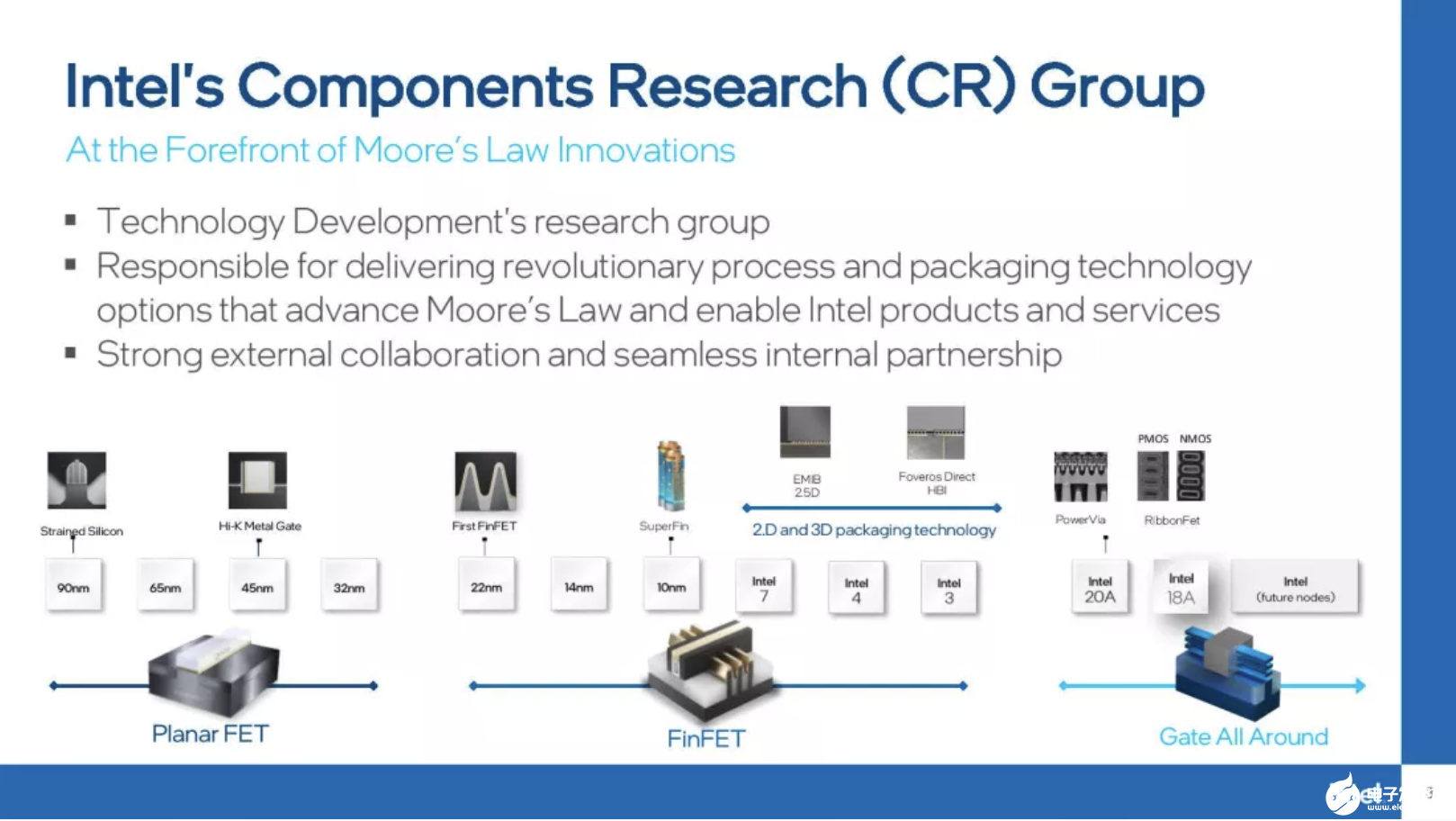

英特尔副总裁兼元件研究(CR)和设计启用部总经理加里·巴顿说:”自晶体管发明以来的75年里,推动摩尔定律的创新继续解决世界上成倍增长的计算需求。在IEDM 2022上,英特尔正在展示突破当前和未来的障碍所需的前瞻性思维和具体的研究进展,满足这种永不满足的需求,并在未来几年保持摩尔定律的活力。”

CR小组的研究已经确定了新的工艺和材料,对推动公司接近其万亿晶体管的里程碑至关重要。该公司最新的混合键合研究显示,与前一年的报告相比有10倍的改进。英特尔提交的材料所展示的其他研究包括使用厚度不超过三个原子的新型材料的设计,可以垂直放置在晶体管上方的存储器,以及对可能对量子数据存储和检索产生负面影响的接口缺陷的更多了解。

英特尔的元件研究小组是公司内部开发新的和突破性技术的领导者。部件研究组的工程师们发明和开发新的材料和方法,支持半导体制造商在持续的战斗中把技术缩小到原子尺度。该小组负责英特尔的极紫外光刻(EUV)技术,该技术对于英特尔继续缩小节点尺寸同时提高整体半导体能力是不可或缺的。该小组的工作和时间表通常比商业上可用的技术领先5到10年。

免责声明:文章内容来自互联网,本站仅提供信息存储空间服务,真实性请自行鉴别,本站不承担任何责任,如有侵权等情况,请与本站联系删除。