在半导体产业的完整产业链中,封装测试是连接芯片设计与终端应用的重要环节,直接关系到芯片的性能、可靠性与成本控制。为了系统厘清封装测试的相关关键问题,以下将以一问一答的形式,从基础概念、核心流程、技术要素、质量控制等多个维度展开详细解析,确保内容的专业性与严肃性。

1. 什么是封装测试?它在半导体产业链中处于哪个环节?

封装测试是半导体制造的后道工序,主要包含 “封装” 与 “测试” 两大核心步骤。其中,封装是将经过晶圆制造环节生产出的裸芯片(Die),通过引线键合、倒装焊等技术与外部引脚或基板连接,并利用封装材料(如环氧树脂、陶瓷等)进行保护的过程,目的是实现芯片与外部电路的电气连接、物理保护及热管理;测试则是在封装前后,通过专业设备对芯片的电学性能、功能完整性、可靠性等指标进行检测,筛选出合格产品并剔除不良品。在半导体产业链中,封装测试处于下游环节,承接上游的晶圆制造,后续直接对接终端电子产品生产(如手机、计算机、汽车电子等领域),是芯片实现商用价值的关键收尾环节。

2. 封装测试的核心流程包含哪些步骤?每个步骤的主要作用是什么?

封装测试的核心流程可分为晶圆级测试、芯片封装、成品测试三大阶段,具体步骤及作用如下:

- 晶圆级测试(Wafer Sorting):在晶圆未切割前,利用探针台与测试机对晶圆上的每个芯片(Die)进行初步电学性能检测,筛选出明显失效的芯片,避免后续封装工序浪费成本,主要检测参数包括电压、电流、电阻、逻辑功能等基础指标。

- 晶圆切割(Die Sawing):将经过晶圆级测试的晶圆,通过金刚石锯片或激光切割技术,分割成独立的合格芯片(Die),切割过程需严格控制精度,避免损伤芯片电路或导致芯片破裂。

- 芯片黏贴(Die Attach):将切割后的合格芯片,通过导电胶或绝缘胶黏贴在封装基板(Substrate)或引线框架(Lead Frame)的指定位置,确保芯片与基板 / 引线框架之间的牢固连接,同时为后续电气连接与热传导奠定基础。

- 引线键合(Wire Bonding)/ 倒装焊(Flip Chip Bonding):这是实现芯片与外部引脚电气连接的核心步骤。引线键合通过金丝、铜丝或铝丝,利用超声波焊接技术将芯片的焊盘(Pad)与封装基板 / 引线框架的引脚连接;倒装焊则是将芯片焊盘朝下,直接与基板上的焊点通过焊料(如焊锡凸点)连接,相比引线键合,倒装焊具有更高的连接密度与更优的电气性能、热性能,适用于高端芯片封装。

- 封装成型(Molding):采用环氧树脂等封装材料,通过模具注塑的方式,将黏贴、键合后的芯片与连接结构完全包裹,形成封装体(Package),起到物理保护(防止灰尘、湿气、机械冲击)、电气绝缘与热扩散的作用,成型过程需控制温度、压力与时间,确保封装体的致密性与稳定性。

- 后固化(Post Molding Cure):将封装成型后的产品放入高温烤箱中进行烘烤,使封装材料充分固化,提升封装体的机械强度、耐热性与耐化学性,避免后续工序中封装体出现开裂或性能衰减。

- 切筋成型(Trim & Form):对于采用引线框架的封装产品,通过冲压设备将引线框架上多余的金属部分(筋条)切除,并将封装体的外部引脚弯折成符合行业标准的形状(如直插式、贴片式),以便后续终端产品的焊接组装。

- 成品测试(Final Test):这是封装测试的最终检测环节,利用测试机与分选机,在不同温度环境(常温、高温、低温)下,对封装完成的成品芯片进行全面的电学性能、功能完整性、可靠性测试,检测参数包括工作频率、功耗、信号完整性、耐压性、稳定性等,最终筛选出合格成品,不良品将被标记并剔除,合格产品则进入后续包装环节。

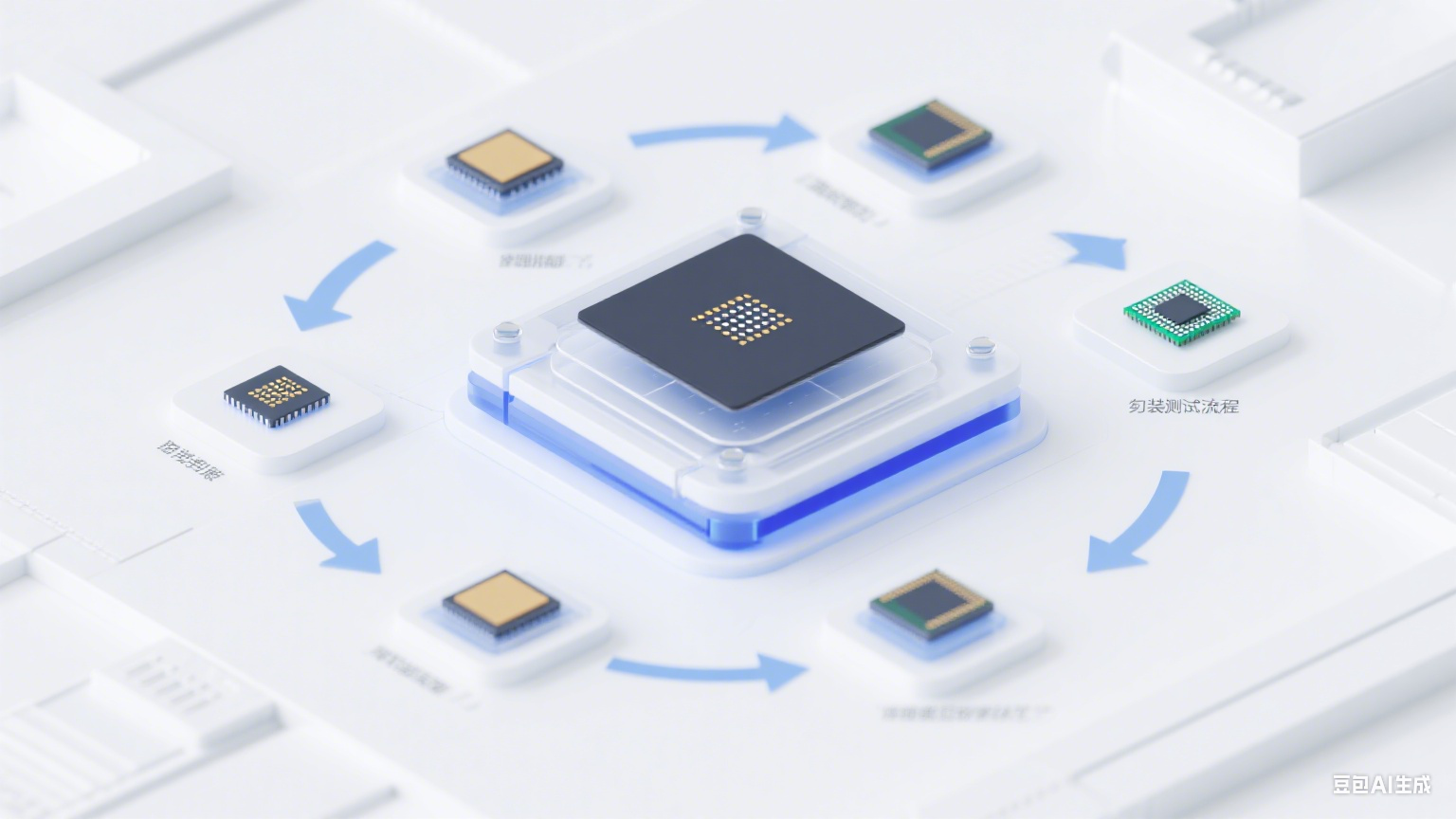

(注:此处为示例图片链接,实际应用中需替换为真实的封装测试流程示意图,图片应包含晶圆切割、芯片黏贴、引线键合、封装成型、成品测试等关键步骤的可视化展示)

3. 封装测试中常用的封装技术有哪些?不同封装技术的适用场景有何差异?

封装测试中常用的封装技术根据芯片类型、性能需求与应用场景,可分为传统封装与先进封装两大类,具体技术及适用场景差异如下:

- 传统封装技术:

- DIP(双列直插封装):引脚从封装体两侧引出,呈直插式结构,工艺简单、成本低,但封装密度低、散热性能较差,主要适用于早期的中低速集成电路(如逻辑芯片、电源管理芯片),目前多用于工业控制领域的低端设备。

- SOP(小外形封装)/SSOP(缩小型小外形封装):引脚从封装体两侧引出,呈贴片式结构,相比 DIP 封装体积更小、封装密度更高,适用于中低速、中等引脚数量的芯片(如单片机、运算放大器),广泛应用于消费电子、汽车电子的普通电路模块。

- QFP(四方扁平封装):引脚从封装体四周引出,呈扁平状,引脚数量较多(通常几十到几百个),封装密度高于 SOP,适用于中等复杂度的数字芯片(如微处理器、FPGA),但引脚间距较小(通常 0.4-0.8mm),对焊接工艺要求较高,多用于计算机主板、工业控制板卡。

- 先进封装技术:

- BGA(球栅阵列封装):引脚以焊球的形式分布在封装体底部,呈阵列状,封装密度高、电气性能优(信号完整性好)、散热性能强,适用于高引脚数量、高工作频率的芯片(如 CPU、GPU、存储器芯片),广泛应用于智能手机、计算机、服务器等高端电子设备。

- CSP(芯片级封装):封装体尺寸与芯片尺寸接近(封装尺寸 / 芯片尺寸比值通常小于 1.2),封装密度极高、寄生参数小,适用于对体积要求严格的场景(如智能手机摄像头模组、可穿戴设备芯片),常见类型包括倒装焊 CSP、引线键合 CSP 等。

- SiP(系统级封装):将多个不同功能的芯片(如处理器、存储器、射频芯片、传感器)与被动元件(电阻、电容、电感)集成在一个封装体内,形成一个完整的功能系统,具有小型化、高性能、低功耗的优势,适用于复杂的系统级应用(如智能手机 SoC、物联网模组、汽车电子控制单元)。

4. 封装测试中的 “测试” 环节具体包含哪些类型?不同测试类型的检测目的是什么?

封装测试中的 “测试” 环节根据测试阶段与检测重点,可分为以下几类,各类测试的检测目的存在明确差异:

- 晶圆级测试(Wafer Sorting):又称中测,属于封装前的初步测试,检测目的是在晶圆切割前筛选出失效芯片,减少后续封装成本浪费,主要检测芯片的基础电学性能(如漏电流、阈值电压、静态电阻)与简单逻辑功能,不涉及复杂的动态性能与可靠性测试,测试环境通常为常温。

- 成品测试(Final Test):又称终测,属于封装后的全面测试,检测目的是验证封装完成的芯片是否满足设计规格要求,确保产品质量,测试内容涵盖电学性能(工作电压、电流、功耗、输出信号幅度)、功能完整性(逻辑运算、数据存储与读取、接口协议兼容性)、动态性能(工作频率、响应速度、信号时序),且需在不同温度环境(常温 25℃、高温 85℃/125℃、低温 – 40℃)下进行测试,模拟芯片在实际应用中的工作条件。

- 可靠性测试(Reliability Test):属于成品测试后的补充测试(部分企业将其纳入成品测试环节),检测目的是评估芯片在长期使用过程中的稳定性与耐久性,筛选出潜在的早期失效产品,确保芯片的使用寿命符合行业标准(通常要求 10 年以上),常见测试项目包括高温高湿存储测试(HTHS)、温度循环测试(TC)、冷热冲击测试(TST)、振动测试、机械冲击测试、静电放电测试(ESD)、电迁移测试(EM)等,测试条件通常比实际应用环境更为严苛。

- 参数测试(Parametric Test):贯穿晶圆级测试与成品测试环节,检测目的是精确测量芯片的电学参数(如晶体管的跨导、电容值、击穿电压、导通电阻),验证芯片的电学特性是否符合设计模型,为芯片性能优化与质量控制提供数据支撑,测试需使用高精度的测试仪器(如半导体参数分析仪),确保参数测量的准确性。

5. 封装测试过程中使用的主要设备有哪些?不同设备的核心功能是什么?

封装测试过程中需使用多种专业设备,各类设备的核心功能与应用环节紧密相关,主要设备及功能如下:

- 探针台(Probe Station):主要用于晶圆级测试环节,核心功能是将晶圆精准定位,并通过探针卡(Probe Card)上的探针与晶圆上芯片的焊盘接触,建立测试机与芯片之间的电气连接,实现对晶圆上每个芯片的逐一检测,设备需具备高精度的定位系统(定位精度通常达微米级)与稳定的探针接触技术,避免损伤芯片焊盘。

- 半导体测试机(Semiconductor Tester):是测试环节的核心设备,分为晶圆级测试机与成品测试机,核心功能是生成测试信号(如电压信号、电流信号、数字逻辑信号),通过探针台或分选机传输至芯片,同时采集芯片的响应信号,对信号进行分析处理,判断芯片是否合格,不同类型的芯片(如数字芯片、模拟芯片、射频芯片)需搭配专用测试机,测试机的性能(如测试速度、信号精度、通道数量)直接影响测试效率与检测准确性。

- 分选机(Handler):主要用于成品测试环节,核心功能是将封装完成的芯片自动上料、传输至测试工位,使芯片与测试机的测试座(Test Socket)精准对接,完成测试后,根据测试结果将合格芯片与不良品自动分类、下料,部分高端分选机还具备温度控制功能(可实现常温、高温、低温测试环境),大幅提升成品测试的自动化程度与效率。

- 晶圆切割机(Die Saw):用于晶圆切割环节,核心功能是将晶圆分割成独立的芯片(Die),根据切割方式可分为刀片切割机(采用金刚石锯片)与激光切割机,刀片切割机适用于大多数晶圆材料(如硅晶圆),成本较低;激光切割机切割精度更高、无机械应力,适用于薄晶圆(厚度小于 100μm)或易碎晶圆材料,设备需具备高精度的运动控制与切割参数调节功能,确保切割后的芯片边缘平整、无损伤。

- 芯片黏贴机(Die Bonder):用于芯片黏贴环节,核心功能是将切割后的合格芯片精准黏贴在封装基板或引线框架上,根据黏贴方式可分为环氧树脂黏贴机与共晶黏贴机(采用金属焊料实现高温焊接),设备需具备高精度的拾取与定位系统(定位精度达微米级),同时控制黏贴压力与温度,确保芯片黏贴的牢固性与一致性。

- 引线键合机(Wire Bonder):用于引线键合环节,核心功能是通过金丝、铜丝或铝丝,将芯片焊盘与封装基板 / 引线框架引脚连接,根据焊接技术可分为超声波键合机与热压键合机,设备需具备高精度的焊丝送丝系统、焊接压力与温度控制功能,确保键合点的强度与电气连接可靠性,键合速度与键合质量直接影响封装生产效率与产品良率。

- 封装成型机(Molding Machine):用于封装成型环节,核心功能是通过注塑方式将环氧树脂等封装材料注入模具,包裹芯片与连接结构,形成封装体,设备主要由注塑系统、模具系统与温控系统组成,需精确控制注塑压力、温度与时间,确保封装体的致密性、尺寸精度与表面质量,避免出现气泡、缺胶、开裂等缺陷。

6. 封装测试的质量控制标准主要有哪些?这些标准如何保障芯片产品质量?

封装测试的质量控制需遵循国际、国家及行业制定的多项标准,这些标准从技术要求、检测方法、流程规范等方面对封装测试过程进行约束,确保芯片产品质量稳定,主要标准及保障作用如下:

- 国际标准:

- JEDEC 标准(联合电子设备工程委员会标准):由美国 JEDEC 组织制定,是半导体行业最权威的标准之一,涵盖封装尺寸、测试方法、可靠性要求等多个领域,例如 JEDEC JESD22 系列标准规定了芯片可靠性测试的具体项目(如温度循环测试、高温高湿存储测试)与测试条件;JEDEC JESD89 标准规定了 BGA 封装的尺寸与引脚布局要求,该标准的通用性确保了不同企业生产的芯片在封装尺寸、测试方法上的一致性,便于终端产品的兼容与组装,同时严格的可靠性要求保障了芯片在长期使用中的稳定性。

- IPC 标准(国际电子工业联接协会标准):主要针对电子组装与封装工艺,例如 IPC-A-610 标准规定了电子组件的可接受性 criteria,涵盖封装体外观、引脚焊接质量等视觉检测要求;IPC-9701 标准规定了半导体封装的热性能测试方法,这些标准为封装测试过程中的工艺控制与质量检测提供了明确依据,帮助企业识别封装缺陷(如封装体开裂、引脚变形、焊接虚焊),确保产品符合行业通用质量水平。

- 国家标准:

- 中国制定了多项半导体封装测试相关国家标准,例如 GB/T 15510-2017《半导体分立器件和集成电路 第 1 部分:总规范》规定了半导体器件的通用质量要求与测试方法;GB/T 26114-2010《半导体器件 机械和气候试验方法》规定了封装后的芯片在机械冲击、振动、温度湿度等环境下的测试方法,这些标准结合国内半导体产业实际情况,对封装测试的质量控制提出了明确要求,保障了国内芯片产品的质量安全与市场准入合规性。

- 企业内部标准:

除了外部标准,大型半导体企业还会制定高于行业标准的内部质量控制标准,例如针对特定芯片(如汽车电子芯片)制定更严苛的可靠性测试条件(如更长的高温高湿存储时间、更宽的温度循环范围),或在封装工艺中增加额外的检测环节(如封装体 X 射线检测、键合点显微镜检测),进一步降低产品不良率,满足高端应用领域(如汽车、航空航天)对芯片质量的严格要求。

这些质量控制标准通过明确封装测试的技术参数、检测流程与合格判定准则,使企业在生产过程中有据可依,避免因工艺参数失控或检测遗漏导致的质量问题;同时,标准的统一性也便于行业内的质量对比与监督,推动整个封装测试行业的质量水平提升,最终保障芯片产品在终端应用中的可靠性与安全性。

7. 封装测试过程中常见的缺陷有哪些?导致这些缺陷的主要原因是什么?

封装测试过程中,受工艺参数、设备精度、材料性能等因素影响,可能出现多种缺陷,常见缺陷及主要原因如下:

- 封装体开裂(Molding Crack):表现为封装体表面或内部出现裂纹,严重时可能导致芯片电路暴露或电气连接失效,主要原因包括:封装材料(环氧树脂)与芯片 / 基板的热膨胀系数不匹配,在温度变化(如后固化、成品测试)过程中产生内应力;封装成型时注塑压力过大或温度过高,导致封装体内部存在残余应力;封装材料本身存在杂质或质量缺陷,降低了材料的抗裂性能。

- 引线键合失效(Wire Bond Failure):表现为键合点脱落、焊丝断裂或键合点接触电阻过大,导致芯片与外部引脚的电气连接中断或性能衰减,主要原因包括:键合机参数设置不当(如焊接压力过小、温度过低、超声波能量不足),导致键合点结合强度不足;芯片焊盘或引线框架引脚表面存在氧化层、油污等杂质,影响焊丝与焊盘 / 引脚的结合;焊丝材料质量不合格(如金丝纯度不足、铜丝存在杂质),或焊丝直径不均匀,导致键合过程中出现焊丝断裂。

- 芯片黏贴偏移(Die Attach Misalignment):表现为芯片黏贴在基板 / 引线框架上的位置偏离指定区域,可能导致后续引线键合无法正常进行,或芯片与基板的热传导路径受阻,主要原因包括:芯片黏贴机的定位系统精度不足(如视觉定位误差过大);黏贴过程中黏合剂(导电胶 / 绝缘胶)涂抹不均匀,导致芯片在黏贴后发生偏移;晶圆切割后的芯片尺寸存在偏差,或基板 / 引线框架的定位标记不清晰,影响黏贴机的定位准确性。

- 封装体气泡(Molding Void):表现为封装体内部存在气泡,可能导致封装体的机械强度下降、散热性能变差,甚至在温度变化时因气泡膨胀导致封装体开裂,主要原因包括:封装材料(

免责声明:文章内容来自互联网,本站仅提供信息存储空间服务,真实性请自行鉴别,本站不承担任何责任,如有侵权等情况,请与本站联系删除。