CPU,即中央处理器,是计算机系统的核心组件,负责执行指令、处理数据并协调其他硬件工作。作为整个计算机的运算和控制中心,其性能直接决定了系统的运行效率和处理能力。从个人电脑到服务器,从智能手机到嵌入式设备,CPU 的存在贯穿了几乎所有计算设备,是信息时代技术发展的重要标志。

CPU 的基本功能可概括为指令执行、数据处理和系统控制三大类。指令执行过程包括从内存中读取指令、对指令进行解码以确定操作类型,再调用相应的运算单元完成操作。数据处理涵盖算术运算(如加减乘除)、逻辑运算(如与或非)及数据移位等操作,这些操作通过内部的运算器实现。系统控制则涉及对内存、输入输出设备的协调,通过总线接口与其他硬件交换信息,确保各组件按时序协同工作。

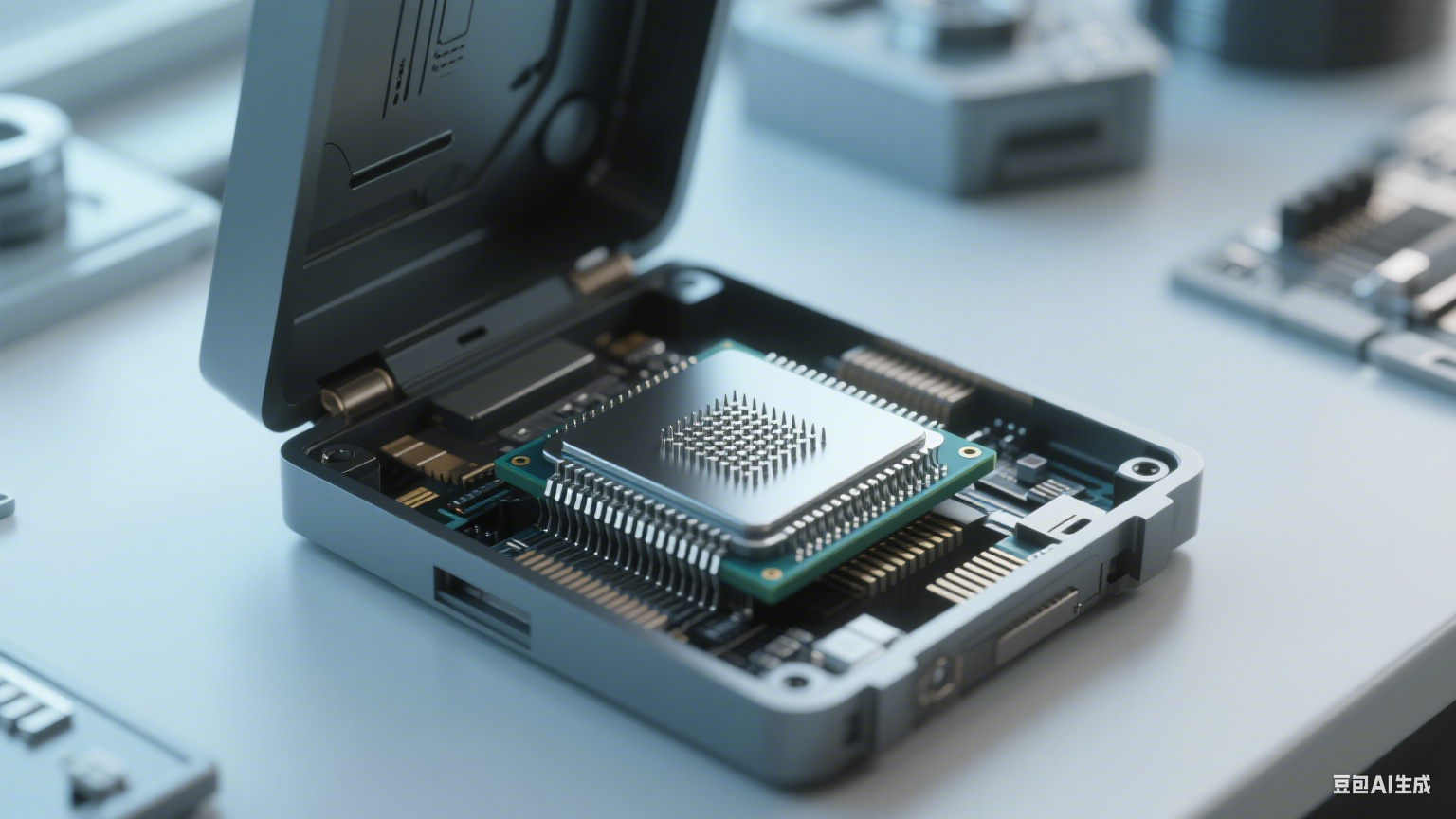

现代 CPU 通常采用超大规模集成电路工艺制造,芯片面积从几十平方毫米到上百平方毫米不等,内部集成的晶体管数量已突破百亿级。这种高度集成化设计不仅提升了运算速度,还降低了功耗和物理尺寸,为移动设备等小型化计算平台的发展奠定了基础。

CPU 的内部结构可分为运算器、控制器、寄存器组和缓存四大核心部分。运算器是执行数据处理的核心单元,包含算术逻辑单元(ALU)、浮点运算单元(FPU)等,其中 ALU 负责整数运算和逻辑判断,FPU 则专门处理高精度浮点计算,适用于科学计算、图形渲染等场景。控制器由程序计数器、指令寄存器、指令译码器等组成,其作用是控制指令的读取、解码和执行顺序,确保整个运算过程按预定流程进行。

寄存器组是 CPU 内部的高速存储单元,用于临时存放指令、数据和地址。根据功能不同可分为通用寄存器(如 eax、ebx 等,用于临时数据存储)、专用寄存器(如程序计数器 PC,用于记录下一条指令的地址)和控制寄存器(如标志寄存器,用于存储运算结果的状态信息)。寄存器的访问速度远高于内存,通常在纳秒级,因此合理利用寄存器能显著提升程序运行效率。

缓存是介于 CPU 与内存之间的高速缓冲存储器,用于缓解 CPU 运算速度与内存访问速度不匹配的矛盾。现代 CPU 普遍采用多级缓存结构,一级缓存(L1)集成在 CPU 核心内部,容量通常为几十 KB,访问延迟仅几个时钟周期;二级缓存(L2)容量为几百 KB 到几 MB,三级缓存(L3)则可达数十 MB,通常为多核 CPU 共享。当 CPU 需要数据时,会先从缓存中查找,未命中时再访问内存,缓存命中率的高低直接影响 CPU 性能,优秀的缓存设计可使命中率达到 90% 以上。

CPU 的工作过程遵循 “取指 – 译码 – 执行 – 写回” 的基本流程,这一过程被称为指令周期。取指阶段,控制器根据程序计数器中的地址从内存读取指令,并将指令存入指令寄存器,同时程序计数器自动递增以指向 next 条指令。译码阶段,指令译码器对指令进行解析,确定需要执行的操作及操作数来源(如寄存器、内存或立即数)。执行阶段,运算器根据译码结果执行相应操作,若涉及内存数据,则通过内存控制器读取或写入数据。写回阶段,将运算结果保存到目标寄存器或内存中,完成一次指令执行。

为提升处理效率,现代 CPU 采用了多种优化技术。流水线技术将指令周期分解为多个独立阶段(如取指、译码、执行、访存、写回),使不同指令的不同阶段可并行处理,理想情况下每个时钟周期能完成一条指令。超标量技术则通过在 CPU 内部集成多个运算单元,实现多条指令的并行执行,如双核 CPU 可同时处理两条指令流,四核 CPU 则支持四条指令流并行。

分支预测技术用于解决程序中条件分支导致的流水线中断问题。CPU 通过分析历史分支行为,预测分支指令的走向并提前预取指令,若预测正确,流水线可继续运行;若预测错误,则需清空流水线并重新取指,因此预测准确率(通常需达到 90% 以上)对性能影响较大。乱序执行技术允许 CPU 在不影响程序逻辑的前提下,调整指令执行顺序,优先执行无依赖关系的指令,充分利用运算单元资源。

衡量 CPU 性能的核心参数包括主频、核心数、线程数、缓存容量、制程工艺等。主频指 CPU 的工作时钟频率,单位为 GHz,代表每秒可执行的时钟周期数,主频越高,理论处理速度越快,但需结合架构效率综合判断,如相同架构下 3.0GHz 的 CPU 性能优于 2.5GHz,但不同架构间则无法直接比较。

核心数是 CPU 内部集成的独立运算核心数量,每个核心可独立执行指令流,核心数越多,并行处理能力越强,适用于多任务处理、视频渲染等场景。线程数是指 CPU 可同时处理的指令流数量,通过超线程技术(如 Intel 的 HT 技术、AMD 的 SMT 技术),单个核心可模拟两个线程,使四核八线程 CPU 能同时处理八个任务,提升多任务环境下的吞吐量。

制程工艺指晶体管的制造工艺,单位为纳米(nm),如 7nm、5nm 工艺。制程越先进,晶体管密度越高(相同面积可集成更多晶体管),功耗和发热也越低,有助于在提升性能的同时控制功耗,如 5nm 工艺较 7nm 工艺晶体管密度提升约 1.8 倍,功耗降低约 30%。

CPU 的架构设计决定了其性能上限和应用场景。CISC(复杂指令集计算机)架构(如 x86 架构)包含丰富的复杂指令,可减少指令数量,但硬件实现复杂,主要应用于个人电脑和服务器。RISC(精简指令集计算机)架构(如 ARM 架构)采用精简指令集,指令长度固定,硬件实现简单,功耗较低,广泛用于智能手机、嵌入式设备等移动平台。

VLIW(超长指令字)架构将多条指令打包成一条长指令,由编译器负责指令调度,适合特定领域(如数字信号处理),但灵活性较差。不同架构的 CPU 在指令集、寄存器结构、内存访问方式等方面存在差异,导致软件无法直接兼容,需通过指令集仿真或重新编译才能跨架构运行。

CPU 的发展历程可追溯至 20 世纪 70 年代。1971 年,Intel 推出世界上第一款微处理器 4004,采用 4 位架构,主频 740kHz,集成 2300 个晶体管,开启了微处理器时代。1978 年,Intel 8086 处理器问世,奠定了 x86 架构的基础,成为个人电脑的主流架构。20 世纪 90 年代,CPU 主频进入 GHz 时代,1999 年 Intel Pentium III 处理器主频突破 1GHz。

21 世纪以来,CPU 发展从追求主频转向多核化,2005 年 AMD 推出首款双核处理器 Athlon 64 X2,标志着多核时代的到来。近年来,随着移动互联网和人工智能的兴起,CPU 与 GPU、NPU 等异构计算单元的融合成为趋势,如苹果 M 系列芯片采用 CPU+GPU+NPU 的集成设计,大幅提升了移动端的综合处理能力。

不同应用场景对 CPU 的需求存在显著差异。个人电脑 CPU 注重单线程性能和兼容性,以应对办公、游戏等场景,主流产品为 Intel Core 系列和 AMD Ryzen 系列,主频通常在 3-5GHz,核心数 4-16 核。服务器 CPU 强调多核心、高可靠性和扩展性,如 Intel Xeon、AMD EPYC 系列,核心数可达 64 核甚至 128 核,支持多路互联和海量内存访问。

移动设备 CPU(如手机、平板)则以低功耗、高能效比为核心指标,ARM 架构的高通骁龙、华为麒麟、苹果 A 系列芯片是典型代表,采用 big.LITTLE 架构(高性能核心 + 低功耗核心),在保证性能的同时延长续航时间。嵌入式 CPU 则注重稳定性和成本控制,常用于智能家居、工业控制等领域,如 ARM Cortex-M 系列、MIPS 架构处理器。

CPU 的散热设计直接影响其性能释放和稳定性。CPU 工作时会产生热量,若散热不良,温度过高会触发降频保护,导致性能下降。桌面 CPU 通常采用风冷散热器(由散热片和风扇组成),高端型号或超频场景则需水冷散热器,通过液体循环带走热量。笔记本电脑受限于空间,多采用超薄热管 + 风扇的散热方案,部分高性能机型还会设计双风扇、多热管的散热模组。

散热性能的关键指标是热设计功耗(TDP),单位为瓦特(W),代表 CPU 持续工作时的平均散热功率,如 TDP 65W 的 CPU 通常比 TDP 125W 的 CPU 发热更少。实际使用中,CPU 瞬时功耗可能超过 TDP,因此散热器的散热能力需略高于 TDP 值,以确保散热余量。

随着技术的不断进步,CPU 的发展面临着物理极限和功耗墙的挑战。根据摩尔定律,晶体管密度每 18-24 个月翻一番,但当制程工艺接近 1nm 时,量子隧穿效应会导致晶体管无法正常工作,传统硅基芯片的发展遭遇瓶颈。为此,行业正探索新材料(如石墨烯、碳纳米管)、新架构(如存算一体、光量子计算)和异构计算等方向,试图突破现有技术限制。

未来 CPU 可能不再单纯追求计算性能的提升,而是向智能化、低功耗、专用化方向发展。面向人工智能场景的专用加速单元将更深度地集成到 CPU 中,边缘计算设备的 CPU 将进一步优化能效比,而通用计算与专用计算的协同,或许会成为下一代计算架构的重要特征。这些探索将如何重塑 CPU 的形态和功能,仍有待时间给出答案。

免责声明:文章内容来自互联网,本站仅提供信息存储空间服务,真实性请自行鉴别,本站不承担任何责任,如有侵权等情况,请与本站联系删除。